Luna: LUT-Based Neural Architecture Achieves 10.95x Faster, 30% More Efficient Qubit Readout

Summarize this article with:

Accurate and rapid qubit readout represents a significant challenge in the development of practical quantum computers, and researchers are actively exploring new methods to improve this critical process. M. A. Farooq, G. Di Guglielmo, and A. Rajagopala, alongside colleagues, present a novel approach called LUNA, a fast and efficient accelerator for superconducting qubit readout. This architecture combines simple, low-cost signal processing with Look-Up Table based neural networks, dramatically reducing both the hardware resources required and the time taken to interpret qubit states.

The team demonstrates substantial improvements over existing methods, achieving up to a ten-fold reduction in hardware area and a 30% decrease in latency, all while maintaining high accuracy, and paving the way for scalable and reliable quantum computing systems. FPGA-Optimized Lightweight Neural Networks for Qubit Readout This research introduces LogicNets, a new approach to qubit readout that combines machine learning with Field-Programmable Gate Arrays (FPGAs) to achieve high fidelity, low latency, and efficient resource utilization. Traditional qubit readout methods often struggle with latency, fidelity, and scalability, but machine learning offers potential improvements if complex models can be efficiently deployed on FPGAs.

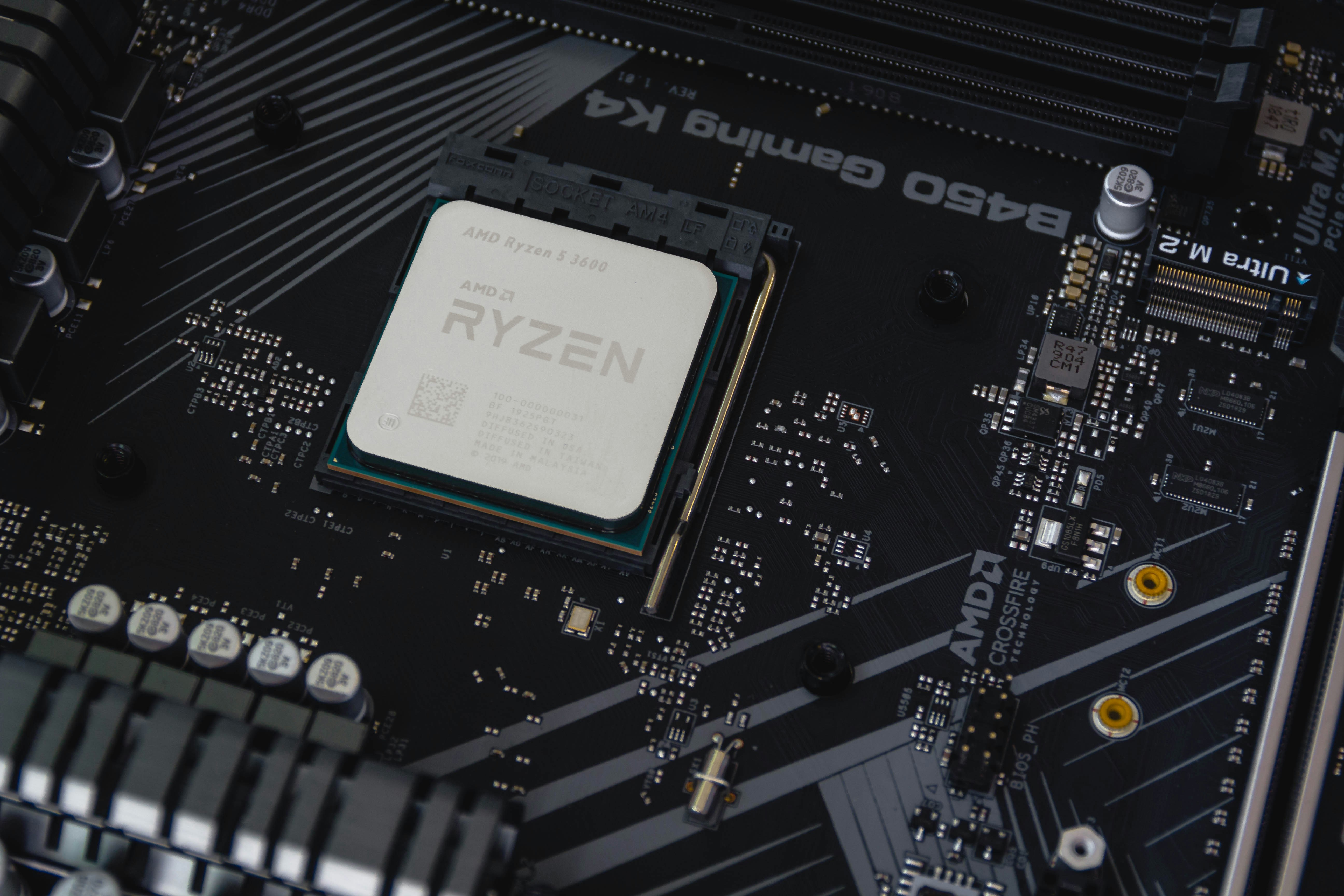

The team co-designs lightweight neural networks with FPGA hardware, focusing on techniques like weightless neural networks and efficient architectures to minimize computational complexity. The training process is guided by FPGA constraints, ensuring the resulting model can be efficiently mapped to the hardware, optimizing dataflow, memory access patterns, and parallelization for maximum performance. A Differential Evolution algorithm automatically discovers optimal network architectures for the FPGA. The results demonstrate that LogicNets achieves state-of-the-art qubit readout fidelity, comparable to or exceeding traditional methods, while significantly reducing readout latency and minimizing FPGA resource usage. The authors provide an open-source framework to foster collaboration and reproducibility, and have validated the approach on a real superconducting qubit system, demonstrating its practical feasibility. LUT Neural Network Accelerates Qubit Readout Scientists have developed LUNA, a novel qubit readout accelerator that significantly improves both speed and efficiency. Recognizing limitations in existing deep neural network (DNN) implementations, which are resource intensive and slow, the team engineered an architecture combining simple integrator-based preprocessing with Look-Up Table (LUT) based neural networks. This approach drastically reduces resource usage while enabling ultra-low-latency inference, crucial for advanced quantum computing systems. To achieve this, the study pioneered a novel integrator-based strategy for preprocessing, replacing traditional methods with a technique that reduces the dimensionality of the input signal with minimal hardware overhead. Scientists then implemented LogicNets, mapping DNN inference directly into FPGA LUTs, eliminating the need for multipliers and digital signal processors by constraining network connectivity, encouraging sparsity, and using quantization during training, allowing each neuron’s function to be extracted as a LUT truth table. A Differential Evolution algorithm efficiently searches the design space and identifies high-quality designs. Experiments demonstrate that LUNA achieves up to a 10. 95x reduction in area and a 30% lower latency, with little to no loss in fidelity compared to state-of-the-art methods. FPGA Accelerates Qubit Readout, Reduces Latency Scientists have achieved a breakthrough in qubit readout acceleration with the development of LUNA, demonstrating significant reductions in area and latency while maintaining high fidelity. The research team implemented a co-designed preprocessing and classification pipeline on an AMD/Xilinx FPGA, achieving up to a 10. 95x reduction in area compared to state-of-the-art implementations and a 30. 9% reduction in inference latency.

The team’s approach utilizes simple integrators for preprocessing, replacing resource-intensive matched filters without compromising fidelity, and employs LogicNets, LUT-based neural networks, for classification. These LogicNets map efficiently to FPGA primitives, enabling ultra-low-latency inference with minimal area usage. A differential evolution algorithm was integrated to identify high-quality design points, further enhancing performance. The system is compatible with the Quantum Instrumentation and Control Kit (QICK), demonstrating its practical applicability.

Efficient Qubit Readout With LUNA Framework This research presents LUNA, a novel hardware-software framework designed to significantly improve the efficiency of qubit state readout in quantum computing systems. By combining integrator-based dimensionality reduction with neural network classifiers implemented as Look-Up Tables, the team achieves substantial reductions in both hardware footprint and processing latency, demonstrating up to a 10. 95-fold decrease in area and a 30% reduction in latency while maintaining high discrimination fidelity, nearing 96%. This advancement is particularly important for scaling quantum processors, as it directly addresses the resource demands of large-scale systems requiring numerous parallel mid-circuit measurements and quantum error correction operations.

The team employed differential evolution to optimise both the preprocessing stage and the structure of the neural network, identifying compact designs that minimise resource usage without compromising performance. 👉 More information 🗞 LUNA: LUT-Based Neural Architecture for Fast and Low-Cost Qubit Readout 🧠 ArXiv: https://arxiv.org/abs/2512.07808 Tags: