Parity-Unfolded Distillation Architecture to Lower Resource Overhead

Summarize this article with:

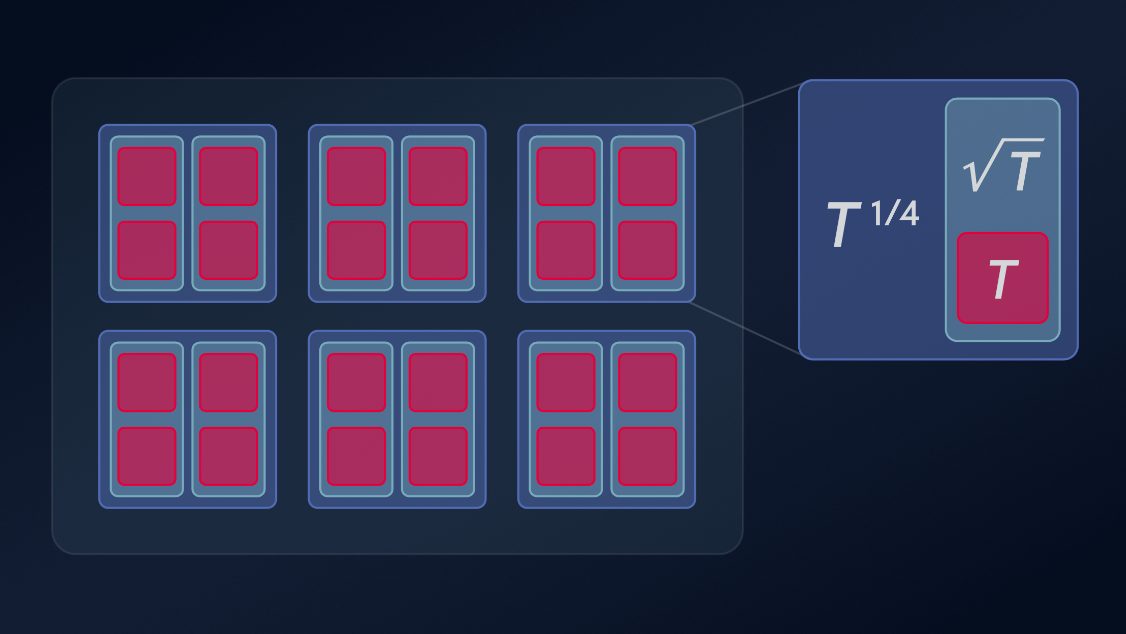

Insider Brief Researchers at ParityQC and the University of Innsbruck introduced a fault-tolerant quantum computing architecture designed to reduce the resource overhead required for universal quantum computation. The proposed “Parity Unfolded Distillation Architecture” aims to make difficult-to-protect non-Clifford quantum gates more practical in two-dimensional quantum chip layouts that rely on nearest-neighbor qubit interactions. The researchers reported that extending beyond the standard Clifford+T gate set with additional higher-level non-Clifford gates could reduce both logical error rates and the number of resources needed for quantum gate synthesis on noise-biased hardware platforms. PRESS RELEASE — A group of physicists at ParityQC and the University of Innsbruck has introduced the Parity Unfolded Distillation Architecture, a fault-tolerant quantum computing scheme that significantly lowers the required resource overhead. Achieving useful and universal quantum computation requires a combination of Clifford gates and at least one non-Clifford gate. While Clifford gates form the robust backbone of quantum error correction and are relatively easy to implement fault-tolerantly in standard schemes compatible with planar layouts, non-Clifford gates are notoriously difficult to protect. They are highly susceptible to noise and typically cannot be applied fault-tolerantly in two-dimensional architectures without significant overhead. The dominant modern approach is magic state distillation, a resource-intensive workaround where many imperfect non-Clifford states are generated and combined into a smaller number of higher-quality non-Clifford states. While the most common approach involves only a single non-Clifford gate known as a T gate, the universal gate set can be further supplemented with additional non-Clifford gates, typically sampled from levels of the Clifford hierarchy. In the latest publication “Parity-unfolded distillation architecture for noise-biased platforms”, a group of researchers at ParityQC and the University of Innsbruck (Konstantin Tiurev, Christoph Fleckenstein, Christophe Goeller, Paul Schnabl, Matthias Traube, Nitica Sakharwade, Anette Messinger, Josua Unger, and Wolfgang Lechner) devised hardware-friendly protocols for distilling various non-Clifford gates in hardware platform dominated by one type of noise. Key features of the proposed architecture include: Climbing up the Clifford hierarchy: The scheme provides a unified framework and constructive schemes for distilling rotation gates from arbitrary level of the Clifford hierarchy. Unfolding to planar layouts: The architecture is compatible with two-dimensional qubit architectures that allow for nearest-neighbor interactions only. While no-go theorems limit the fault-tolerant implementation of gates from higher levels of the Clifford hierarchy to higher-dimensional qubit connectivity, the combination of biased noise and the introduced parity-unfolding procedure allows to implement all such gates in two-dimensional layouts. Efficient gate synthesis: An arbitrary rotation of a qubit state requires decomposition into a finite sequence of discrete gates. We show that supplementing the standard Clifford+T gate set with parity-unfolded gates from higher levels of the Clifford hierarchy allows to reduce both the overall resource overheads and the total error of logical gates, hence improving two most important metrics for universal fault-tolerant quantum computing. The pre-print “Parity-unfolded distillation architecture for noise-biased platforms”, authored by Konstantin Tiurev, Christoph Fleckenstein, Christophe Goeller, Paul Schnabl, Matthias Traube, Nitica Sakharwade, Anette Messinger, Josua Unger, and Wolfgang Lechner, is now available here.

Matt Swayne LinkedIn With a several-decades long background in journalism and communications, Matt Swayne has worked as a science communicator for an R1 university for more than 12 years, specializing in translating high tech and deep tech for the general audience. He has served as a writer, editor and analyst at The Quantum Insider since its inception. In addition to his service as a science communicator, Matt also develops courses to improve the media and communications skills of scientists and has taught courses. matt@thequantuminsider.com Share this article: